It’s been a while since my last post and as one of the aims was to use a blog to provide more updates, I need to get busy.

Block diagrams are excellent

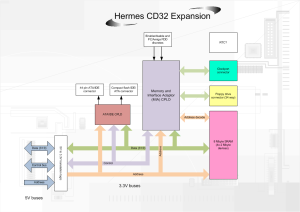

The design is still progressing, it’s just taking a bit of time. One of the first important steps for me is to sketch a block diagram of the system, here is one I made earlier:

It might not look the most exciting diagram but it helped to plan the design. From this it was easy to get a feel for the number of I/O pins for the CPLDs, it showed me where I need the 5V/3.3V logic translation and what discretes were needed.

The design has three discretes/jumpers. The first is an enable/disable jumper (or switch). If A game refuses to work with the extra RAM, you can easily disable the whole card. PATA should not be affected but is to be confirmed.

There are another two discretes are related to the floppy drive interface. The first input tells the CPLD if either a PC(default) or Amiga floppy drive is connected. This is so I can crossover the important signals (CHNG/RDY) and generate the RDY signal. The other discrete input/jumper is if a duall floppy drive cable is used with a twist, it will again allow me to crossover signals. The floppy interface by default supports PC floppy drives as they are cheaper to obtain.

The final option is a 4MB/8MB RAM selector. To cut costs, this would allow a system with 4MB of RAM. May not be used.

From this diagram I sketched out (but have not shown here) the top level blocks of the Memory and Interface Adaptor (MIA) CPLD. This helps me plan a logical flow for the CPLD. Without this I would not have thought of some of the extra switch inputs.

Changing CAD software

This might seem crazy and it has delayed me a little bit but I took the decision to change the CAD software I use. Since 2002 I have used Cadsoft EagleCAD, a fine tool I know well. I currently use V5.11, which is stable and does most of what I need. One of the limitations is PCB area. Up until now, a 160x100mm PCB area has been sufficient. This design might be greater than that.

I currently have a standard license, which costs 690 Euros+VAT. To move to the Professional edition, for a larger PCB area, the license is 1385 Euro+VAT! As a registered user, my upgrade costs are slightly reduced. The software upgrade costs would out-strip any money I make from this project, so a cheaper solution was required, enter DesignSpark PCB.

Designspark has had a learning curve, sometime steep but it was not unexpected. I have had to create a few schematic and layout symbols but that is inevitable and a good chance to learn. The online help is Ok but a bit lacking in some areas (took a while to find how to easily edit existing library symbols and download many of them). No schematic tool is perfect though. In addition to Eagle CAD I also use Mentor Graphics schematic tools in my day job, sometimes I try shortcuts from one tool in another.

One area I do plan to use Designspark PCB for is the 3D modelling and mechanical design. It easily creates a 3D view of the PCB, from within the package. With Eagle I have to run a script, export to Sketchup and render, not as easy as one click. In the future, I will put the Designspark Mechanical training to use and export my PCB into a 3D model. Ok I need to create a basic model of say a CD32 enclosure and a clockport card but it will help. No pain no gain.

I have some ideas of how to make a product tester, this has helped with the design a little as it made me added a few test signals to the edge connector and also how to easily verify a batch of boards.

Progress to date

This will be asked so I might as well say how it is going.

The basic schematics I had have been re-drawn in Designspark. It was mainly some TTL logic, RAM and a CPLD.

The bulk of the remaining schematic work depends on the MIA CPLD design. This will drive the device pinout, taking into account PCB routing. Future efforts will focus on this device. My CPLD design skills are Ok, they need to improve, one of the aims of this project.

I will not have a prototype PCB by the end of June 2014 as I planned. A finished schematic diagram would be good and a mostly finished CPLD is my aim by the end of June.

There is still some static timing analysis to be done, around the CPU and SRAM interfaces but I need to finish some of this to constrain the CPLD timing.

The plan after it has been tracked is for 2-4 prototypes, they will get comprehensively tested and from there, depending on interest, look at production.

I hope to have another update early July.

Ian

I have a few additions about which you may have forgotten.

The fact that CD32 is not very reliable CD Drive and replacing it is not possible.

So I suggest you do two IDE ports – HDD and CD Drive.

If possible, should that be CD-ROM port on the expansion card, the system seen as a native.

Moreover, it is desirable that CD Drive was visible in BIOS natively.

For example, in my CD32 is not working CD Drive. I can not find a replacement.

And the power port – 12+5 (Molex). For connect power cord CD-Rom.

May by change HDD on the microCD?

By the way I could help the project financially … I could make a pre-order.

microCD=microSD

About CAD software.

Maybe pCad + CircuitWorks + SolidWorks?

The design is fixed at the moment as I’m desperately trying to avoid feature creep.

A PATA (IDE) CD drive would complicate things. There’s no support in the ROM, thus requiring a driver as cd32.device only supports the custome CD interface. The other issue is that it would draw more current that the stock CD32 power supply can provide. One of my design goals was to keep it close to a stock system.

You can replace the laser assembly and the FFC cable that connects the CD drive, as I have had to do on my CD32.

MicroSD or SDcard would make the logic a bit trickier. It would need a high speed SPI interface or 4 bit parallel interface for the card, neither of which I currently have a design for, Compact Flash I do have.

Thank you for the offer of a pre-order, I have funds for the development phase and on conclusion of that, will look into funding the production, depending on interest levels.

Ian

I still insist on introducing me to the list of pre-order.))

Assembling CD-Drive on sale I can not find.

Over time, the CD-Drive completely disappear from the market. And one with a third party device would not be bad.

I’m not talking about the current project. Maybe you have time to create a device with the Notebook CD-Rom – Amiga CD32 CD interface?

At work I deal with CAD Software. And I can give you access to SolidWorks + CircuitWorks. Completely legal.

CircuitWorks allows you to import IDF of PCB Software and continue to work with them in 3D.

Are you interested?

About MicroSD – I understand that the CF is much easier (it is very similar to the IDE), I question the miniature.

About additional functionality – is required to make a RGB output.

Since CD32 on by default, it is not soldered, and you have to take the signal directly to the motherboard.

As far as I remember scheme CD32, RGB is available on the expansion port.

Hi, I’ve got a CD32 and SX32 and love the machine, but would still be interested in your project especially if it lets me put the CF card externally. My biggest issue with the CD32 is running games at 60hz. Because the vertical sync is so far of the NTSC spec of 59.94 my TV won’t lock to it properly and the scrolling stutters. I always wondered if the external clock option could be used to fix this, is it something you have considered?

Hi Matt,

The suggestion of allowing a CF card to be inserted externally is something to consider when I get to the final PCB layout. It could reside on the right hand side of the board, allowing for a cutout in the case. Will bear this in mind.

With regard to the 60Hz/59.95Hz NTSC issue, I’ve never seen a TV so fussy. The original RS170A NTSC specification had 60Hz, the later SMPTE170M standard defined 59.96 Hz. The only time a TV might get upset if you are using YPbPr rather than RGB or S-Video as the Analog Front Ends (AFE) are fussy in YPbPr mode. This is not something I could fix as the Amiga derives all timing from the 28.x MHz master crystal.

I would be interested in a pre order.

Dita

i want it for my cd32 :]

Hi Ian – is there any update? Hope its coming along good…

Am interested too in a board when complete.